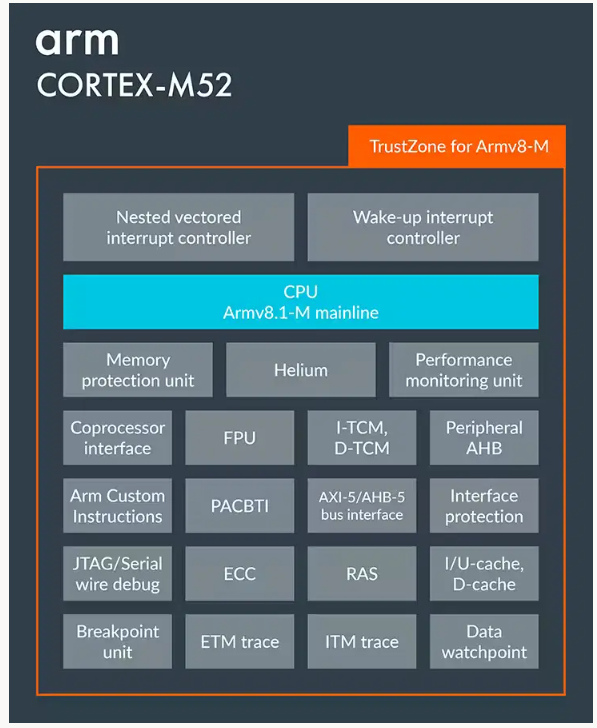

Arm Cortex-M52是一款采Arm Helium 技术的新型微控制器内核,旨在将AI功能引入更小、成本更低的物联网设备,而不是基于Arm Cortex-M55内核的SoC,Arm Cortex-M52架构如下图所示。

Arm Cortex-M52主要特性和规格:

1. 架构 – Armv8.1-M

2. 总线接口

a. AMBA 5 AXI 32位或AMBA 5 AHB

32位主系统总线

b. AMBA 5 AHB 32位外设总线

c. AMBA 5 AHB 32位TCM接入总线

3. 管道 – 4级管道

4. 安全

a. Arm TrustZone技术,具有多达8个

区域的可选安全单元

b. 可选支持PACBTI扩展

5. 内存保护

6. DSP扩展 – 32位DSP/SIMD扩展

7. 浮点单元(FPU) – 可选 FPU,支持半精度(fp16)、单精度(fp32)和双精度(fp64)浮点运算。

8. 加速器支持

a. 可选的协处理器接口,支持多达8

个协处理器单元,用于自定义计算加速器

b. 可选Arm自定义说明

9. 指令缓存 – 高达64kB,带ECC

10. 数据缓存 – 高达64kB,带ECC

11. 指令TCM(ITCM) – 最大16MB,带 ECC

12. Data TCM(DTCM – 最大16MB,带 ECC

13. 中断 – 集成嵌套向量中断控制器,支持多达480个中断和不可屏蔽中断。优先级数可配置从8到256。

14. 唤醒中断控制器 – 内部和/或外部WIC,用于将处理器从状态保持、电源门控或所有时钟停止时唤醒。

15. 低功耗支持

a. 架构定义的睡眠和深度睡眠模式

b. 集成了等待事件和等待中断指令,

具有退出时休眠功能

c. 睡眠和深度睡眠指示信号

d. 多个电源域,可选存储器和逻辑保

持支持

e. 性能效率:4.3CoreMark/MHz和

1.6DMIPS/MHz

16. 调试

a. 硬件和软件断点

b. 性能监控单元

c. 跟踪

17. 鲁棒性

a. ECC on指令缓存、数据缓存、指令 TCM、数据 TCM

b. 双核锁步

c. 总线接口保护

d. 可靠性、可用性和可维护性扩展

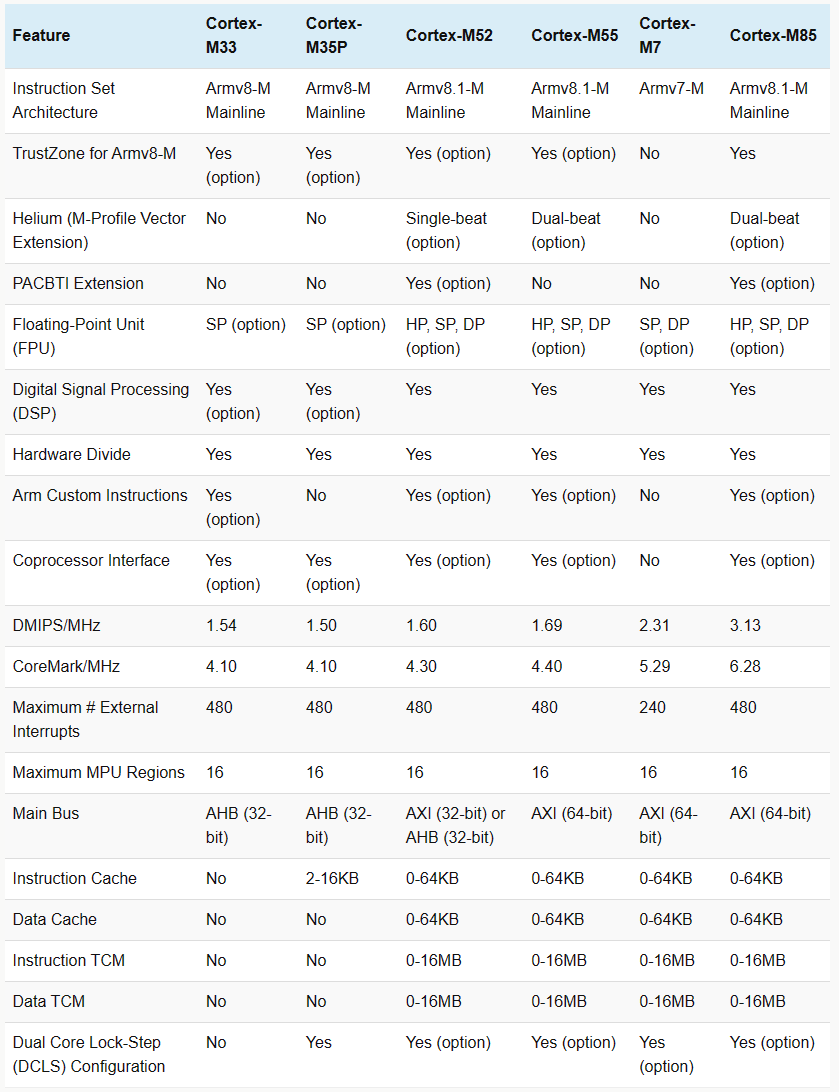

Cortex-M52的架构与Cortex-M55的架构几乎相同,除了显示PACBTI模块不是 DSP模块外以及“AXI-5 master”字符串被“AXI-5/AHB-5 总线接口”取代。两者并没有许多差异,Arm提供了所有Arm Cortex-M处理器的比较表如下图所示。

Cortex-M52和 Cortex-M55之间存在差异,新器件的主总线是32位,而 Cortex-M55 支持64位AXI总线。这也许可以解释为什么Arm表示Cortex-M52为汽车和工业控制、预测性维护和可穿戴传感器融合中的AIoT应用提供从Cortex-M33和 Cortex-M4 的简化迁移路径。

Cortex-M55和Cortex-M85内核相比,Cortex-M52提供了更高的效率、更小的占用空间和更低的价格,但代价是性能较低。但该公司仍然声称“开发人员可以从 ML和DSP性能的提升中受益,与前几代 Cortex-M相比,ML的性能提升高达5.6倍,数字信号处理性能提升高达2.7倍”。

Arm Cortex-M52将取代由CPU、DSP和 NPU组成的传统边缘AI解决方案,这些解决方案需要三个独立的工具链、编译器、调试器等......使开发人员能够使用单一工具链和其他开发工具,为传统、DSP和 ML工作负载编写统一的开发流程。它还与Cortex-M55和Cortex-M85内核保持完全软件兼容。由于实际芯片可能需要一段时间才能上市,因此Cortex-M52将很快在Arm虚拟硬件上推出,以提前启动软件开发。