前言

2023年Zephyr开发者大会(ZDS)于6月27日至30日在捷克布拉格隆重举行。与以往两次不同,本次ZDS由Zephyr项目规划和管理,并作为首届嵌入式开源峰会(EOSS)的一部分进行。在这个令人期待已久的盛会中,全球Zephyr开发者们共同探讨了Zephyr实时操作系统(RTOS)的最新技术与发展趋势。作为一款开源、灵活和可扩展的嵌入式实时操作系统,Zephyr项目在2014年由英特尔发起,2016年作为Linux基金会项目正式面向公众启动,得到了全球范围内的广泛关注和采用。

ZDS 2023共70余个技术报告,涵盖了使用指导与展示、新功能与技术、架构修改与操作系统、多核异构与虚拟化、模拟器、测试、工业流程与代码管理、安全性、应用案例、工具与调试等丰富多样的内容。湖大嵌入式实验室的小伙伴们将对本次大会的所有技术报告进行逐一收集、整理与分享,尽最大努力为Zephyr开发者提供ZDS 2023技术报告的开发经验、实践成果以及解决方案的参考。

今天分享第15篇技术报告,题目为:

“Zephyr时钟系统重构”

作者简介

Moritz Fischer ,谷歌软件工程师。Moritz多年来一直是Linux内核FPGA管理器子系统的维护者。他参与 过系统引导、固件、 BIOS、内核等多方面的项目。

文章简介

基于Zephyr设备树的时钟描述适用于现有驱动程序的一个子集,这些驱动程序大致分为两类:支持编译 时频率已知的输入时钟的驱动程序,以及使用时钟控制API配置时钟的驱动程序。在这篇文章中,作者简 要描述了Zephyr的时钟系统以及其为优化时钟系统所做的尝试。除此之外,作者还与社区就如何推进统 一API进行了讨论,使所有驱动程序都可以与固定时钟和动态时钟一起工作。

相关名词

ASIC(Application Specific Integrated Circuit):专用集成电路。

IP(Intellectual Property):知识产权,半导体产业将IP定义为用于ASIC、ASSP和PLD等当中,并且 是预先设计好的电路模块。

PLL(Phase Locked Loop(PLL):锁相环,集成在时钟芯片中,用于完成时钟频率的转换(分频,倍 频)。

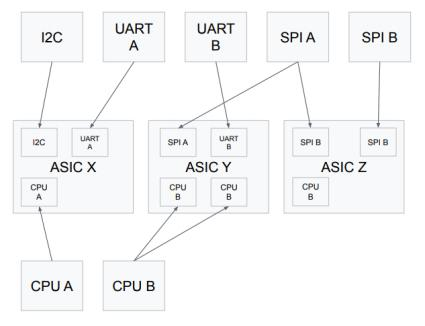

不同ASIC的IP集成方式不同,如图1所示,对每种ASIC进行固件重写显然是不可能的。

图1不同ASIC的IP集成方式

从硬件上来说,典型的ASIC集成差异包括:总线的宽度和种类,对IP功能的扩充与裁剪,重置方式以及 时钟系统。

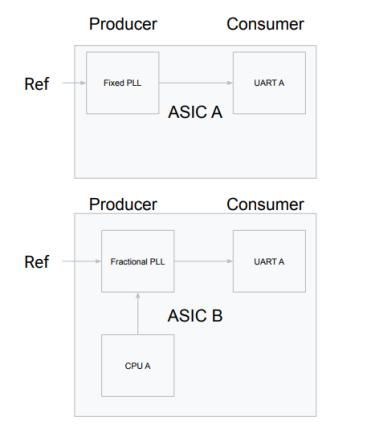

ASIC中的所有IP都需要时钟系统才能触发状态的切换,从而正常运行。可以将时钟系统和依赖时钟系统 运行的硬件比喻成生产者和消费者模型,消费者需要从生产者那里获得信息或控制生产者,如图2所示, 生产者是固定频率的时钟系统或小频率的时钟系统,消费者是UART,它的输出波形取决于输入时钟速 率。消费者不需要知道生产者的内部情况,因此时钟系统提供的API应该尽可能简单,比如用来设置和获 得始终速率的setrate()和getrate()。

图2 不同ASIC的IP集成方式

Zephyr支持三种类型的时钟,分别是:

基于现阶段Zephyr时钟驱动程序可重用性不高这一事实,作者提出了几点关于重构Zephyr时钟系统的设 想,以期望Zephyr在时钟系统上具有和Linux时钟系统相同的表现。

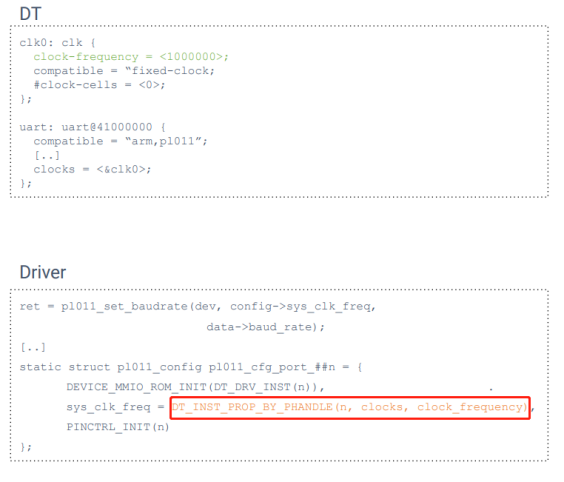

1. 为固定时钟配置驱动程序。因为现阶段对固定时钟的配置都是在编译时完成的,并且可以通过宏直 接从设备树文件中获取时钟信息,因此固定时钟模块相当于一直处在打开的状态。所以需要为其配 置一个驱动程序,来控制其状态。

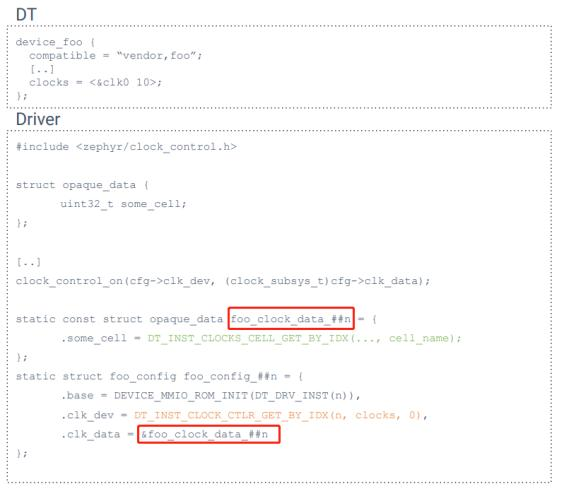

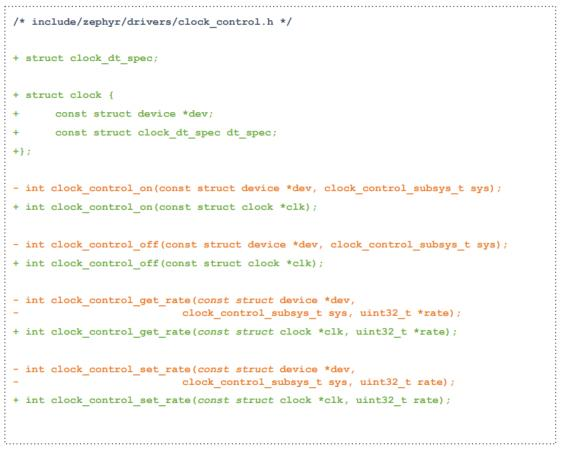

2. 定义clock结构体。定义一个封装了给定时钟的所有信息的结构体clock,并修改所有的时钟系统 API,将clock结构体作为它们传递的参数。如下代码所示:

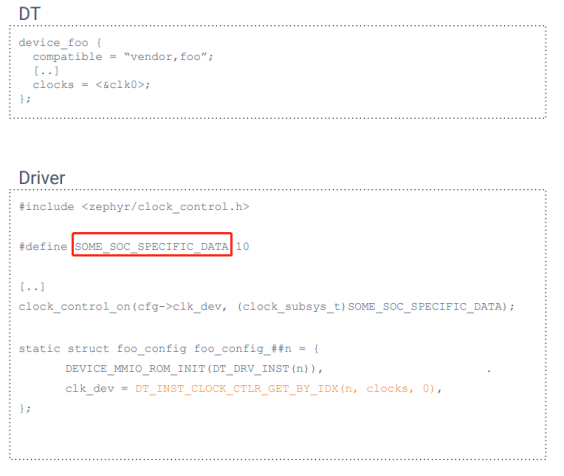

3. 为驱动程序提供一组新的helper函数,从而完成数据的解耦功能,提高代码的重用性。